Программное обеспечение качества Catapult® для управлениядля разработкиоптимизации

Добавить в папку «Избранное»

Добавить к сравнению

fo_shop_gate_exact_title

Характеристики

- Функция

- качества, для управления, для разработки, оптимизации, для проверки, синтеза

- Применение

- процесса, потока, ПЛИС

Описание

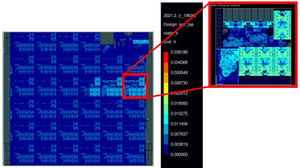

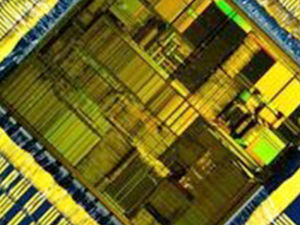

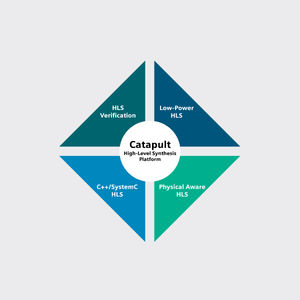

Компания Catapult обладает широчайшим портфелем решений для проектирования аппаратного обеспечения на основе высокоуровневого синтеза (HLS) на языках C++ и SystemC. Физически-ориентированный режим Catapult с несколькими ВЦ, оценка и оптимизация низкого энергопотребления, а также ряд ведущих решений для верификации делают Catapult HLS больше, чем просто "C to RTL".

Клиенты Catapult обсуждают использование HLS в реальном мире

В последние несколько лет наблюдается бурный рост применения HLS для проектирования микросхем, вызванный увеличением сложности проектирования и верификации, а также давлением времени выхода на рынок. Catapult HLS позволяет разработчикам быстрее выводить свои микросхемы на рынок за счет сокращения общего потока проектирования и верификации.

Решения для высокоуровневого синтеза Catapult

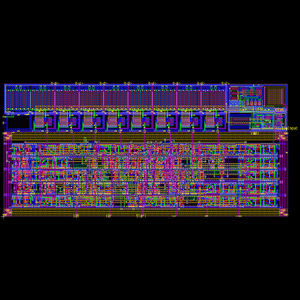

Решения Catapult High-Level Synthesis обеспечивают поддержку языков C++ и SystemC, независимость от FPGA и ASIC, оценку и оптимизацию мощности ASIC, а также новейшие технологии оптимизации площади и производительности с учетом физики.

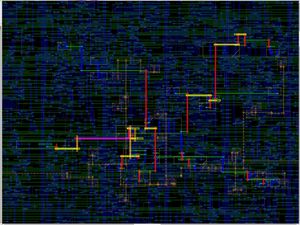

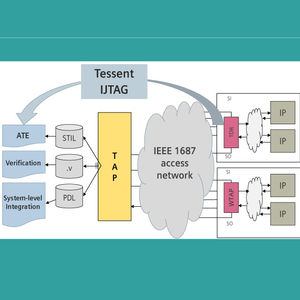

Решения Catapult для высокоуровневой верификации

Ускорьте процесс высокоуровневой верификации (HLV) с помощью известных и надежных методов, используя платформу Catapult HLV. Сократите общее время выполнения верификации SoC и затраты на нее на 80 %, используя высокоуровневую проверку дизайна, код/функциональное покрытие и статические и формальные методы.

Высокоуровневый синтез Catapult

Узнайте, как платформа для высокоуровневого синтеза и верификации Catapult позволяет вам делать больше и лучше. Узнайте об AI/ML, глубоком обучении, компьютерном зрении, коммуникациях, видео и многом другом. Инструменты высокоуровневого синтеза и верификации (HLS и HLV) компании Siemens обеспечивают необходимое вам конкурентное преимущество.

---

Каталоги

Для этого товара не доступен ни один каталог.

Посмотреть все каталоги SIEMENS EDAРасширенный поиск

- Программное обеспечение для автоматизации процесса

- Программное решение для управления

- Программное решение для анализа

- Программное решение процесса

- Программное решение Windows

- Программное обеспечение CAO

- Программное обеспечение для управления

- Программное обеспечение режим реального времени

- Подключенное программное обеспечение

- Программное решение для разработки

- Программное решение 3D

- Программное обеспечение для интерфейса

- Промышленное программное решение

- Программное обеспечение для измерений

- Программное обеспечение качества

- Программное обеспечение моделирования

- Программное решение для визуализации

- Автоматизированное программное решение

- Программное решение для сети

- Программное решение развития

* Цены указаны без учета налогов, без стоимости доставки, без учета таможенных пошлин и не включают в себя дополнительные расходы, связанные с установкой или вводом в эксплуатацию. Цены являются ориентировочными и могут меняться в зависимости от страны, цен на сырьевые товары и валютных курсов.