- Роботизация - Автоматизация - Информатика

- Промышленная информатика

- Микропроцессор 2 ядра

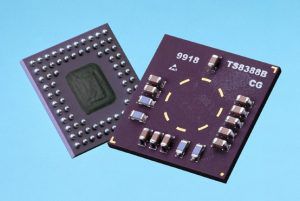

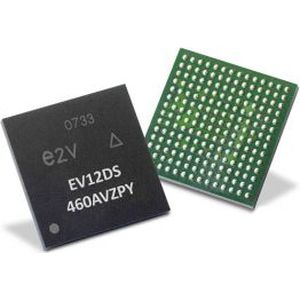

- e2v scientific instruments

Микропроцессор 2 ядра PC8572E

Добавить в папку «Избранное»

Добавить к сравнению

fo_shop_gate_exact_title

Характеристики

- Число горелок

- 2 ядра

Описание

ТЕЛЕФОНЫ

- Двойные встроенные ядра e500, масштабирование до 1,5 ГГц

- 6897 MIPS на частоте 1500 МГц (расчетный кристалл 2.1)

- 36-разрядная физическая адресация

- Усовершенствованная поддержка отладки аппаратного и программного обеспечения

- Устройство с плавающей запятой двойной точности

- Группа управления памятью

- Интегрированный кэш L1/L2

- L1 Кэш: 32 КБ Данные и кэш-память инструкций 32 КБ с кэшем инструкций

Поддержка блокировки линии связи

- Общий кэш L2: 1 МБ с ECC

- L1 и L2 Когерентность аппаратного обеспечения

- L2 Конфигурируемый как SRAM, кэш и транзакции ввода-вывода могут

спрятаны в кэш-памяти L2

- Встроенный контроллер памяти DDR с полной поддержкой ECC,

Поддерживаю:

- 333 МГц Частота синхронизации (667 МГц), 64-разрядная, 1,8 Вольт

SSTL, DDR2 SDRAM

- Частота синхронизации 400 МГц (до 800 МГц), 64-разрядная,

1.5V SSTL, DDR3 SDRAM

- Платформа ускорения работы приложений

- Продвинутый TLU

- Интегрированная поддержка движка безопасности DES, 3DES, MD-5,

SHA-1/2, AES, RSA, RNG, Kasumi F8/F9 и ARC-4

Алгоритмы шифрования

- Интегрированный PME (регулярное выражение)

- Пакетная дефляция двигателя

- Интегрированный механизм безопасности с XOR

- Четыре В-чип, трехскоростные Ethernet-контроллеры Поддержка

10 и 100 Мбит/с и 1 Гбит/с Ethernet/IEEE 802.3 Сети Ethernet/IEEE

с MII, RMII, GMII, SGMII, RGMII, RTBI и TBI Physical

Интерфейсы и IEEE 1588

- Ускорение контрольной суммы TCP/IP и усовершенствованное QoS

Особенности

- Регулирование расхода без потерь

- Универсальные входы/выходы

- Последовательное высокоскоростное соединение RapidIO и PCI Express Высокоскоростное соединение

Интерфейсы

- Ткань коммутатора сети (OCeaN) с встроенным микросхемом (OCeaN)

- 133 МГц, 32-разрядный, 3.3V I/O, Локальная шина с памятью

Контроллер

- Двойной интегрированный DMA-контроллер

- Двойной I

2

C и DUARTS

- Программируемый контроллер прерываний

- IEEE 1149.1 Порт JTAG для тестирования доступа

- 1,1 В Напряжение ядра с 3,3 В/2,5 В/1,8 В I/O

- 1023-контактный PBGA пакет

---

Каталоги

Для этого товара не доступен ни один каталог.

Посмотреть все каталоги e2v scientific instrumentsДругие изделия e2v scientific instruments

Semiconductors

* Цены указаны без учета налогов, без стоимости доставки, без учета таможенных пошлин и не включают в себя дополнительные расходы, связанные с установкой или вводом в эксплуатацию. Цены являются ориентировочными и могут меняться в зависимости от страны, цен на сырьевые товары и валютных курсов.